在當今高速發展的電子技術領域,可編程邏輯技術已成為驅動創新的核心引擎。可編程邏輯電子技術方案,以其高度的靈活性、可重構性和強大的并行處理能力,為從消費電子到工業控制、從通信網絡到人工智能的廣泛領域提供了堅實的技術基礎。本文將深入探討可編程邏輯技術文庫的價值,解析其作為電子技術開發核心方案的關鍵作用。

一、可編程邏輯技術文庫:知識聚合的智慧寶庫

可編程邏輯技術文庫并非簡單的資料匯編,而是一個系統化、結構化、持續更新的專業知識體系。它通常涵蓋硬件描述語言(如VHDL、Verilog)、可編程邏輯器件(如FPGA、CPLD)的架構原理、開發工具鏈(如Vivado、Quartus)的使用指南、IP核資源、設計范例、時序分析、功耗優化策略以及最新的行業協議標準(如PCIe、DDR、以太網)應用方案。

對于開發人員而言,一個優質的技術文庫意味著:

- 快速入門與學習路徑:為新手提供從基礎概念到高級應用的清晰學習曲線,縮短技術掌握周期。

- 問題解決的參考系:當遇到具體的設計挑戰,如時序收斂困難、資源利用率優化、接口調試時,文庫中的案例與經驗分享能提供直接參考。

- 最佳實踐與設計范式:匯集了經過驗證的可靠設計方法,幫助開發者規避常見陷阱,提升代碼質量與系統穩定性。

- 技術前沿的窗口:及時收錄新技術、新器件(如Versal ACAP、高性能FPGA)的特性與應用,確保開發方案的前瞻性。

二、可編程邏輯電子技術方案:實現靈活與高效的開發范式

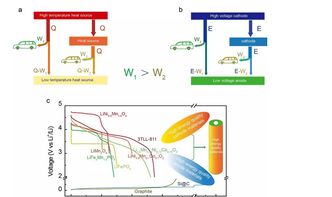

基于可編程邏輯器件的技術方案,其核心優勢在于“軟硬件協同設計”與“現場可重構”。這徹底改變了傳統ASIC(專用集成電路)設計周期長、成本高、風險大的模式。

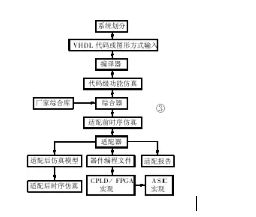

典型的電子技術開發方案流程包括:

- 需求分析與算法建模:在Matlab/Simulink或高層次綜合(HLS)環境中進行算法驗證與性能評估。

- 硬件設計與描述:使用HDL將算法轉化為可綜合的硬件電路描述,這是技術文庫提供核心支持的階段。

- 功能仿真與驗證:通過完善的測試平臺(Testbench)進行邏輯功能驗證,確保設計符合預期。

- 綜合、布局布線與實現:利用開發工具將代碼映射到目標器件的具體資源上,并優化時序和面積。

- 板級調試與系統集成:將生成的比特流文件下載到實際硬件中,進行實時調試,并與處理器(如ARM核)、外設等集成,形成完整系統。

創新方案體現在:

- 異構計算加速:利用FPGA的并行流水線特性,為AI推理、圖像處理、金融計算等提供遠超通用處理器的能效比。

- 原型驗證與敏捷開發:在流片之前,使用FPGA搭建ASIC或SOC的功能原型,大幅降低開發風險和成本。

- 可升級的硬件系統:產品出廠后,仍可通過更新比特流文件來修復漏洞、增加功能或提升性能,延長產品生命周期。

三、電子技術開發:在可編程邏輯平臺上實現跨越

以可編程邏輯為核心的技術開發,正朝著更智能化、集成化和系統化的方向演進。

- 設計抽象層次提升:從傳統的RTL級設計,向基于C/C++/OpenCL的高層次綜合(HLS)和基于平臺的嵌入式軟件開發(如使用Xilinx Vitis或Intel oneAPI)遷移,讓軟件工程師也能高效利用硬件并行能力。

- 系統級芯片(SoC)與片上網絡(NoC):現代可編程邏輯器件集成了多核處理器、高速接口、AI引擎等,開發重點轉向復雜的軟硬件任務劃分、協同設計與系統優化。技術文庫需要相應擴展到嵌入式Linux驅動開發、實時操作系統、異構通信等領域。

- 驗證復雜度的挑戰:隨著系統復雜度指數級增長,驗證工作占用了超過70%的開發精力。基于UVM的方法學、形式化驗證以及硬件仿真(Emulation)等技術,成為技術文庫中不可或缺的高級內容。

- 生態與社區共建:開源硬件項目(如RISC-V在FPGA上的實現)、豐富的第三方IP市場以及活躍的開發者社區,與技術文庫相輔相成,共同構成了繁榮的開發生態。

###

可編程邏輯技術文庫與可編程邏輯電子技術方案,共同構成了現代電子技術開發的雙翼。前者是持續積累與傳承的知識土壤,后者是靈活高效、應對萬變的技術利器。對于企業和開發者而言,持續建設和利用好技術文庫,深入掌握可編程邏輯開發方案,意味著能夠更快地將創新想法轉化為穩定、可靠、具有競爭力的產品,從而在瞬息萬變的市場中占據先機。隨著芯片工藝的不斷進步和應用場景的持續深化,可編程邏輯技術必將在電子技術開發的藍圖中,扮演愈加關鍵的角色。